Hey readers, I have a quick announcement before getting to the core of the post. This project will be continuing through the Fall semester! Quite excited. I did not get where I wanted in the summer session and my professor offered me the opportunity to continue this as a Project II class. Great news! More fun ahead.

Well, since the end of the summer session I've been busy finalizing my guitar amp build, just finished last week. My professor and I agreed that building the amp unmodified first would be a good idea, that way I am actually see what kind of voltages I will be dealing with as I design the VCF.

Here's it the completed amp!

It sounds great. I was blown away it worked when I first switched it on. I've heard horror stories of people spending a week tracking down incorrect wiring or bad components on their first builds. Phew!

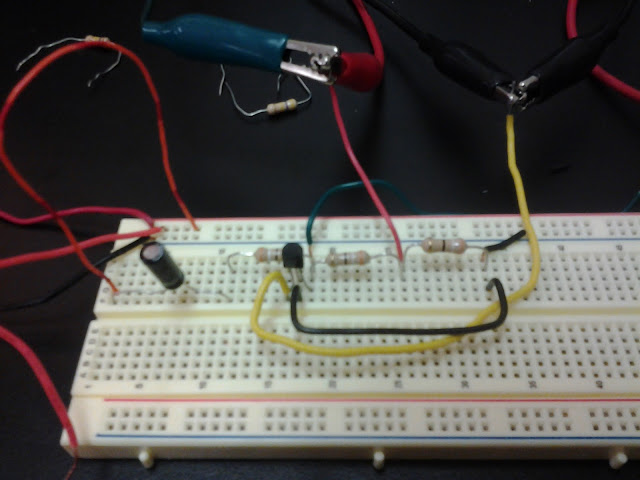

Now, I do have a prototype VCF, it is not at all designed to be placed inside the amp, it was more of a proof of concept. And it does work as a VCF under certain conditions. One of those conditions being an input signal with a magnitude of around 200mV-500mV, any greater or lesser voltage causes the transistor to enter saturation and the circuit no longer functions as a VCF. It also has a rather small frequency range/sweep.

Have a look:

I don't have a schematic for this yet. I'll scan in my paper draft when I get the chance. I plan to modify this design within the week. I want to see if I can increase the filter frequency range by placing another FET in series with the first. The FET's I am using have a rather small ohm range, from around 70 ohms to 800 ohms. I will be ordering some different FET's to experiment with this week as well. I need to start some PSPICE simulations soon. We'll see. I have not worked with FET's in PSPICE before.

Well that's all for now,

Mark

Tuesday, August 27, 2013

Saturday, August 3, 2013

Voltage-Controlled Filter Design Theory

Heya folks. I'm currently in the lab at school testing out a simple voltage-controlled filter. I'll show you that in another post soon. But first, I want to share my thought process thus far. I sat down the other night and began writing everything I knew about designing a voltage-controlled filter so I knew what blanks needed to be filled. That writing is below.

Simple RC Filter:

Simple RC Filter:

This circuit attenuates particular frequencies (in this case, low frequencies) depending on the value of the components. With a variable capacitor or resistor, the specific frequencies can be attenuated or swept through. A simple mechanical device, called a potentiometer is a variable resistor that can be used in this way. The tone knobs on the front of any typical guitar amp utilize this phenomena.

If the Thevenin resistance and total capacitance of the filter are known, then the corner/cutoff frequency of the filter can be mathematically calculated with the following equation:

F_c = 1/(2*pi*R*C)

For low and high pass filters, the cutoff frequency is the frequency at which the output magnitude equals 0.707 times the input magnitude. Or in layman's turn, the frequency where the filter starts working.

So, with this filter theory behind us, let's talk about designing a voltage-controlled filter. We need some device to replace a potentiometer. So it needs to be a three-pronged device where one input controls the flow of current between two of the other inputs. Well this sounds eerily like our good friend the Field-Effect Transistor!

An FET is an electrical device made of semi-conducting material (commonly silicon). The voltage between the gate and source (V_gs) controls the current flow through the source and drain (I_ds), well not entirely. An FET can operate in two different regions. In the saturation region, the drain current is nearly independent of the drain/source voltage. In the ohmic region, the drain current does depend on the drain/source voltage.

My understanding as of now is that small changes in V_gs result in different resistances between the drain and source, however, you've got to be careful to stay operating in the ohmic region, that depends on what V_ds is. Man this is confusing. The circuit I'm testing now seems to be working this way. I just arbitrarily chose some resistors and a capacitor. I need to sit down and derive a circuit with specific characteristics, then test it in the lab. I was just getting familiar with the topology in the lab today.

Here are the documents I have been studying today. Most of what I've discussed has come from them.

http://hyperphysics.phy-astr.gsu.edu/hbase/electric/filcap.html (Basic high pass filter theory)

http://users.ece.gatech.edu/~lanterma/sdiy/datasheets/transistors/vishay_fet_cvr_an.pdf (The circuit I'm testing today is a modification of Figure 7 in this publication)

http://graffiti.virgin.net/ljmayes.mal/comp/vcr.htm (This discusses making an FET operate linearly in the ohmic region)

Well, I've got o quit for today. More again Monday.

-Mark

If the Thevenin resistance and total capacitance of the filter are known, then the corner/cutoff frequency of the filter can be mathematically calculated with the following equation:

F_c = 1/(2*pi*R*C)

For low and high pass filters, the cutoff frequency is the frequency at which the output magnitude equals 0.707 times the input magnitude. Or in layman's turn, the frequency where the filter starts working.

So, with this filter theory behind us, let's talk about designing a voltage-controlled filter. We need some device to replace a potentiometer. So it needs to be a three-pronged device where one input controls the flow of current between two of the other inputs. Well this sounds eerily like our good friend the Field-Effect Transistor!

An FET is an electrical device made of semi-conducting material (commonly silicon). The voltage between the gate and source (V_gs) controls the current flow through the source and drain (I_ds), well not entirely. An FET can operate in two different regions. In the saturation region, the drain current is nearly independent of the drain/source voltage. In the ohmic region, the drain current does depend on the drain/source voltage.

My understanding as of now is that small changes in V_gs result in different resistances between the drain and source, however, you've got to be careful to stay operating in the ohmic region, that depends on what V_ds is. Man this is confusing. The circuit I'm testing now seems to be working this way. I just arbitrarily chose some resistors and a capacitor. I need to sit down and derive a circuit with specific characteristics, then test it in the lab. I was just getting familiar with the topology in the lab today.

Here are the documents I have been studying today. Most of what I've discussed has come from them.

http://hyperphysics.phy-astr.gsu.edu/hbase/electric/filcap.html (Basic high pass filter theory)

http://users.ece.gatech.edu/~lanterma/sdiy/datasheets/transistors/vishay_fet_cvr_an.pdf (The circuit I'm testing today is a modification of Figure 7 in this publication)

http://graffiti.virgin.net/ljmayes.mal/comp/vcr.htm (This discusses making an FET operate linearly in the ohmic region)

Well, I've got o quit for today. More again Monday.

-Mark

Subscribe to:

Comments (Atom)